### Tutorial 1 - SS2022 Communication Systems and Protocols

Institut fuer Technik der Informationsverarbeitung - ITIV Dr.-Ing. Jens Becker • Matthias Stammler

## Task 1: Quadrature Amplitude Modulation

A) What is the difference between the PSK and the QAM modulation technique?

PSK modulates only the signal phase while QAM additionally modulates the amplitude of the signal.

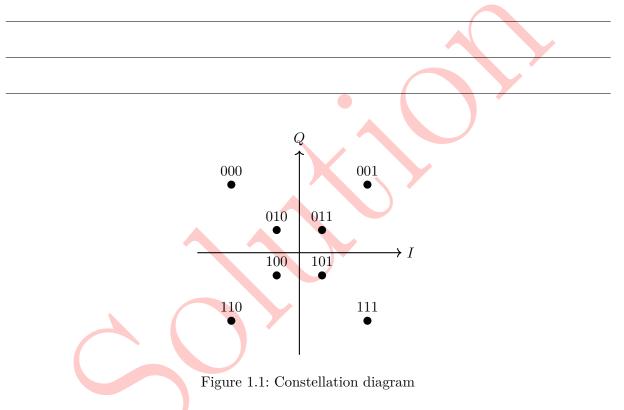

B) Figure 1.1 shows a constellation diagram for a digital modulation technique. Which type of modulation is used here? Which properties of the signal can be varied with this modulation type?

Modulation type: 8-QAM Varied properties: Phase and Amplitude 8

1

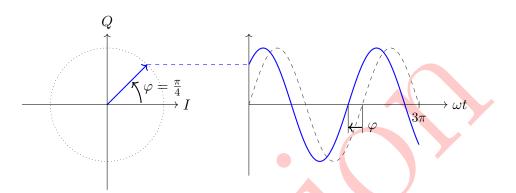

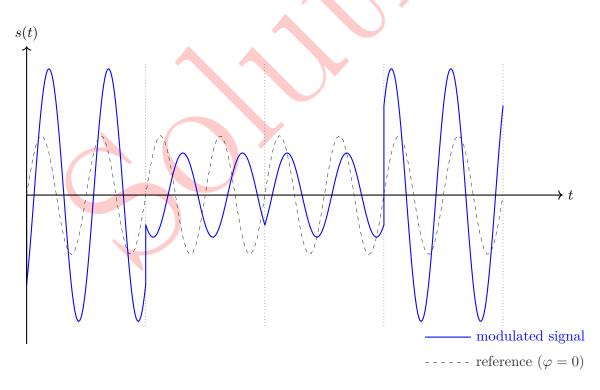

C) The symbol constellation from Figure 1.1 is now used by a transmitter to modulate data bits on a carrier. The phase  $\varphi$  of the signal is defined relative to a sine reference signal as shown in Figure 1.2. A receiver device now picks up the modulated signal which is plotted in Figure 1.3. Which bits have been transmitted by the sender? Demodulate the signal and write down the resulting bit-stream.

#### Transmitted bits:

$\begin{aligned} (\varphi &= -\frac{\pi}{4}, \text{HIGH amplitude}) & 111 \\ (\varphi &= -3\frac{\pi}{4}, \text{LOW amplitude}) & 100 \\ (\varphi &= -\frac{\pi}{4}, \text{LOW amplitude}) & 101 \\ (\varphi &= \frac{\pi}{4}, \text{HIGH amplitude}) & 001 \end{aligned}$

Figure 1.2: Phase difference of a sine signal compared to a reference signal (dashed line  $\hat{=}$  reference signal).

Figure 1.3: A modulated signal which uses the constellation from Figure 1.1 on the preceding page.

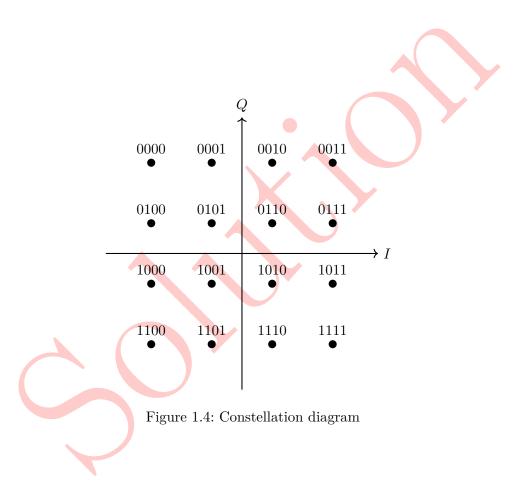

D) Now, a signal is modulated with the constellation diagram from Figure 1.4 and transmitted on a coaxial cable. The sender is able to generate a maximum voltage amplitude  $U_{max}$  of  $\pm \sqrt{72} V$ . Calculate the acceptance radius  $r_a$  for the symbols in the constellation diagram.

From the constellation diagram geometry:  $(2 \cdot U_{max})^2 = (3 (2r_a))^2 + (3 (2r_a))^2$

$(2 \cdot U_{max})^2 = 72 r_a^2$

$$r_a^2 = \frac{(2U_{max})^2}{72}$$

$$r_a = \sqrt{\frac{(2U_{max})^2}{72}}$$

Insert numbers:  $r_a = \sqrt{\frac{4\cdot72}{72}} V = \sqrt{4} V = 2 V$

## Task 2: Reflection on wires

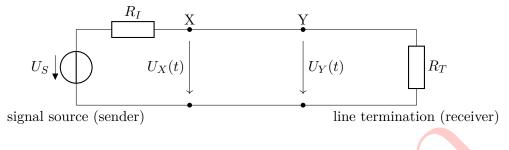

A setup consisting of a voltage source with an internal resistance  $R_I = 50\Omega$  as sender and a receiver with  $R_T = 175\Omega$  is shown in Figure 2. The DC resistance of the line is zero, the characteristic impedance  $Z_0$  is  $75\Omega$ .

Figure 2.1: Test setup

At the time t = 0 the voltage  $U_s$  of the sender changes from 0V to 5V and is constant afterwards. The run time of a wave on the wire is  $t_d$ .

A) What is the value of the voltage at point X at the time t = 0?

At the time of t = 0 the wave only "sees" a series connection of the internal resistance  $R_I$  and the wave impedance Zw.

$U_X(0) = \frac{U_S}{R_I + Z_0} \cdot Z_0 = \frac{5V}{50\Omega + 75\Omega} \cdot 75\Omega = 3V$

B) Which voltage value appears at the points X and Y after an infinite amount of time?

After an infinite amount of time the system is in a steady state, the voltages at points X and Y are identical. When neglecting the DC resistance of the wire a series connection of  $R_I$  and  $R_T$  remains.

$U_X(\infty) = U_Y(\infty) = \frac{U_S}{R_I + R_T} \cdot R_T = \frac{5V}{50\Omega + 175\Omega} \cdot 175\Omega = 3.\overline{8}V$

C) Calculate the voltages at the points X and Y at the times  $t = 0 \dots 5t_d$ . Neglect all transient events, use ideal rectangular impulses for calculation.

6

1

1

Calculation of the reflection factors

- End of wire:  $r_e = \frac{R_T Z_0}{R_T + Z_0} = \frac{175\Omega 75\Omega}{175\Omega + 75\Omega} = 0.4$

- Begin of wire:  $r_b = \frac{R_I Z_0}{R_I + Z_0} = \frac{50\Omega 75\Omega}{50\Omega + 75\Omega} = -0.2$

In general:

- Voltage at point X for time t:  $U_X(t) = U_Y(t-1) + r_b \cdot [U_Y(t-1) U_X(t-2)]$

- Voltage at point Y for time t:  $U_Y(t) = U_X(t-1) + r_e \cdot [U_X(t-1) U_Y(t-2)]$

$\Rightarrow U_X(0) = 3V, \ U_Y(1) = 4.2V, \ U_X(2) = 3.96V, \ U_Y(3) = 3.864V, \\ U_X(4) = 3.8832V, \ U_Y(5) = 3.89088V$

# Task 3: TTL Technology

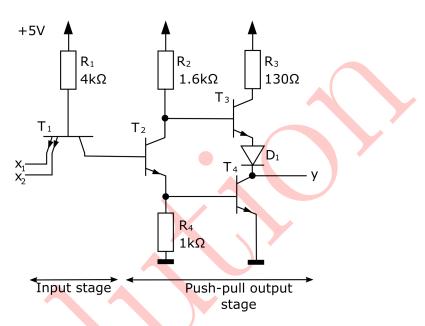

A) Insert the logic level (HIGH, LOW) of the output and the state of the transistors (conducts, blocks) into the table 3.1 according to the input configuration  $x_1$  and  $x_2$  at the standard TTL output driver in figure 3.1.

Figure 3.1: standard TTL output driver

| $x_1$ | $x_2$ | $T_1$ | $T_2$ | $T_3$ | $T_4$ | y |

|-------|-------|-------|-------|-------|-------|---|

| Low   | Low   | ON    | OFF   | ON    | OFF   | Н |

| Low   | High  | ON    | OFF   | ON    | OFF   | Н |

| High  | Low   | ON    | OFF   | ON    | OFF   | Н |

| High  | High  | OFF   | ON    | OFF   | ON    | L |

Table 3.1: Logic Level

B) List two advantages when using TTL drivers.

High currents are possible;

Little energy is consumed while static

© ITIV 2022 Communication Systems and Protocols Tutorial 1 - SS2022

3

$\mathbf{2}$